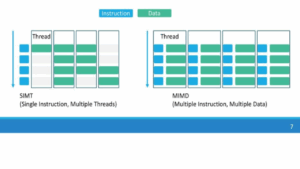

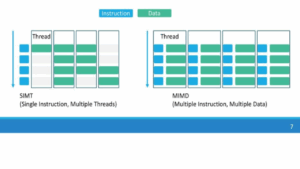

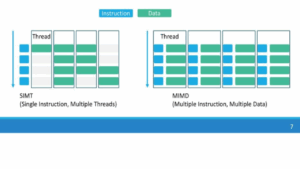

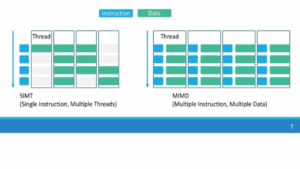

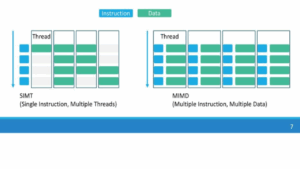

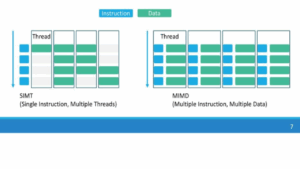

Pezy Computing presented its SC4s processor, a large‑die, 5nm chip that embraces a Multiple Instructions Multiple Data (MIMD) design rather than the mainstream SIMD approach. The chip, fabricated by TSMC, features a die of roughly 556 mm² and aims to deliver hundreds of semi‑autonomous cores that can operate independently. Simulated workloads, including DGEMM and the Smith‑Waterman genome‑alignment algorithm, show substantial gains in power efficiency and performance compared with Pezy’s earlier SC3 design. While the results are still based on simulations, the company plans to move toward a successor using a sub‑3nm process.

Read more →